Nguyên văn bởi binhdt04

Xem bài viết

Thôi bác ơi, sư phụ gì thời đại này nữa. Sư phụ là cái gì cũng biết hết, tớ thì không.

EE thì tại Mỹ không ai biết về fab hết (thời tớ còn trong trường, chưa có lớp nào về cái này hết. Giờ thì không rõ). Lần đầu tiên tớ thấy wafer là do qua học lớp material của engineer. Cái này dành chung cho dân ME, CE và EE. Không phải lớp này dậy về wafer hay fab, mà trong lớp này có phòng lab cho dân ME học, họ đang nghiên cứu về cách mài wafer cho mỏng lại. Món này kêu là back lap / back lapping. Vì thấy nên ghé qua coi chơi mới biết thôi. Dân học về mấy món này thường là đám bên material science.

Tiện đây nói về nó luôn.

Khi wafer đã hoàn thành thì họ mài cho nó mỏng lại trước khi cắt ra từng miếng để qua khâu đóng gói. Khâu mài này không nằm trong fab, vì nó dơ (bụi) và lúc đó wafer đã được bọc trên mặt với lớp bảo vệ rồi, cho nên khó mà bị làm cho hư hỏng lắm.

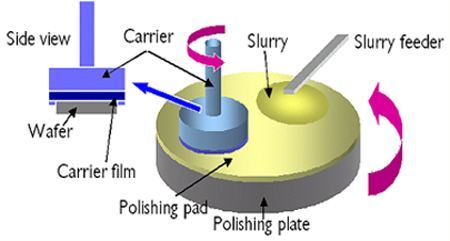

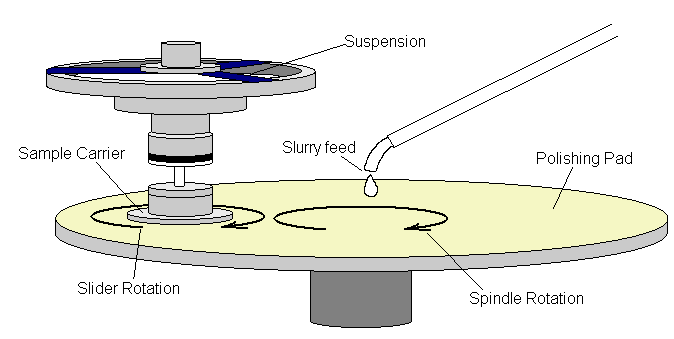

Máy mài thì dùng sức ép đè wafer xuống một tấm "đá mài", trên đó họ đổ một chất nhìn rất giống nước củ sắn, kêu là slurry. Slurry có những hột silica thật mịn nằm trong dung dịch và hoạt động giống như một loại giấy nhám và sẽ bào mỏng mặt dưới của wafer. Khi nước slurry này khô lại thì cũng y như nước bột sắn bị khô. Nó sẽ đóng mảng trắng và sẽ bể thành bụi trắng nếu đụng vô. Vì vậy mà không được nằm trong fab. Tuy nhiên có một khâu rất giống cái này nhưng lại nằm trong fab kêu là CMP. Sẽ nói về nó sau.

Họ bào wafer từ 30mils xuống chừng 6-15 mils. Tới lúc này vì wafer quá mỏng nên nó sẽ cong như bánh tráng phơi sương nếu cầm lên. Nghe thì thấy lạ vì silicon matrix thuộc loại cứng như kim cương thì làm sao mà cong được. Thật ra thì nó cũng giống như cáp quang thôi, khi kéo sợi thủy tinh cho mỏng lại thì nó có thể cuộn lại được.

Em cũng không để ý lắm nhưng hôm nay đọc bài của bác thấy đề cập tới, em muốn hỏi là bác có biết loại này không, nếu được bác chia sẻ nhé!

Em cũng không để ý lắm nhưng hôm nay đọc bài của bác thấy đề cập tới, em muốn hỏi là bác có biết loại này không, nếu được bác chia sẻ nhé!

Comment