Noise trong cmos là một vấn đề không mới được trình bày rất kỹ trong các sách. Tớ nghĩ tốt nhất bạn nên đọc sách thì tốt hơn, và đầy đủ hơn là mọi người trình bày ở đây. Nhiễu ảnh hưởng chủ yếu đến những mạch cần khuếch đại tín hiệu yếu (vì tín hiệu mạnh rồi thì nhiễu không còn là vấn đề nữa), nên chủ yếu người ta quan tâm đến nhiễu ở mạch LNA (Low Noise Amplifier). Các mạch LNA này người ta cũng đã viết rất nhiều trong các sách, bạn có thể đọc về nó thêm. Nếu bạn có gì thắc mắc trong sách có thể hỏi cụ thể.

Thường thì người ta chọn một mạch chuẩn nào đó rồi dựa theo đó thiết kế mạch LNA. Việc chọn W/L cũng dễ thôi. Với những mạch cần nhiễu thấp thì người ta dùng minimum length channel nên cứ chọn transistor có L nhỏ nhất là được. Việc sử dụng minimum length channel phải để ý đến hiệu ứng short channel effect. Nó có mấy điểm đáng chủ ý. Thứ nhất là output impedance của transistor nhỏ. Thứ hai là matching giữa các phần tử rất kém. Thứ ba là công thức tính dòng điện là I=Vsat*Cox'*W*(VGS-VTH-VDS,sat) không phụ thuộc vào L và là hàm bậc một theo VGS. Cách thiết kế mạch sử dụng minimum length channel bạn cũng có thể đọc thêm trong sách.

Về việc chọn W thường là để xác định dòng. Ví dụ như LNA của các mạch cao tần thường có cảm L. Giá trị của điện cảm này quyết định khoảng tần số hoạt động. Còn dòng điện chạy qua điện cảm lại quyết định điểm làm việc tĩnh được xác định bằng giá trị W của transistor. Về mạch cascode thì mạch này thường được sử dụng để khuếch đại các tín hiệu ở tần số "hơi" cao. Sở dĩ mạch cascode được dùng ở khoảng này vì dù sao mạch cascode cũng chỉ là mạch khuếch đại common source nên không thể dùng vào làm mạch khuếch đại cao tần được. Tuy nhiên nó có cái hay là tần số làm việc của mạch cascode gần như tương đương với tần số làm việc của mạch khuếch đại CS thông thường. Bên cạnh đó để tăng tần số làm việc người ta dùng minimum length channel transistor để giảm nhỏ điện dung ký sinh. Tuy nhiên điều này làm cho trở kháng ra của transistor khá nhỏ. Mạch cascode giúp tăng trở kháng ra của transistor nên vẫn duy trì được hệ số khuếch đại cao.

Trong số các loại nhiễu thì nhiều nhiệt là loại không thể loại bỏ được gần như có thể coi là nền nhiễu không phụ thuộc vào tần số làm việc. Nhiễu 1/f rất mạnh ở mức tần số thấp khoảng từ 100 KHz trở xuống. Ở mức thấp nhiễu 1/f có thể lên đến 5-6 dB có thể nói là rất mạch. Để tránh nhiễu 1/f thì bạn chỉ cần để mạch làm việc ở tần số cao hơn là đủ sau đó tín hiệu ở mức này chuyển trực tiếp sang số rồi xử lý. Tớ lấy ví dụ như bạn thiết kế một chip RF. Tần số RF có thể là mức 1 GHz, còn tần số IF là 1 MHz. Băng thông của tín hiệu giả sử như là 100 KHz. Như vậy khi bạn chuyển tín hiệu IF từ tương tự sang số bạn không gặp vấn đề với nhiễu 1/f. Ngoài ra bạn cũng có thể sử dụng những linh kiện có mức nhiễu nhỏ ví dụ như thay vì dùng silicon thì có thể dùng AsGa... hoặc dùng native transistor...

Thông báo

Collapse

No announcement yet.

Analog IC design

Collapse

X

-

Em yêu cầu một bài viết về noise trong CMOS được không ạ? các nguồn noise-nguyên nhân của noise? các kĩ thuật giảm noise thường áp dụng.

Việc thiết kế size của linh kiện W/L, Gm ảnh hưởng thế nào đến noise ko? lắp cascode..etc..

Leave a comment:

-

Chào bạn Rommel.de,

Mình làm về analog nhiều chứ không phải là digital nên mình chỉ nói những cái gì mình hiểu, và có thể nó sẽ không chính xác. Spyglass của Atrenta cũng như MVRC của synopsys hay Conformal LEC LP của cadence, là những công cụ hỗ trợ cho thiết kế lowpower đối với IC số. Tuy nhiên MVRC chẳng hạn thì không hỗ trợ cho các công nghệ cũ, hình như nó chỉ dùng cho 90nm trở xuống thì phải. Tóm lại các công cụ dạng này kiểm tra khá nhiều thứ và có một thứ là "low power analysis". Trong đó nó sẽ kiểm tra tất cả các net giữa các power domain xem có levelshift không, có isolation cell không.... Cái hay là mình có thể tự định nghĩa các rules cho phần này.Nguyên văn bởi Rommel.de Xem bài viếtBạn có thể giới thiệu sơ lược về phần mềm spyglass được không. Tớ chưa bao giờ dùng cái này cả. Ví dụ trong bài toán của mình thì mình hy vọng nó sẽ phát hiện ra lỗi net1 không có isolation cell. Đọc report của nó thì mình có thể sẽ chú ý đến anh này và phát hiện ra.

Ví dụ trong bài toán của mình thì mình hy vọng nó sẽ phát hiện ra lỗi net1 không có isolation cell. Đọc report của nó thì mình có thể sẽ chú ý đến anh này và phát hiện ra.

Bọn mình có làm full chip verification chứ, nếu không thì ai cho tape-out được. Cái này tốn nhiều thời gian lắm, nên các khối tương tự toàn dùng ở dạng behavior model, nên những lỗi kiểu này vẫn có cơ hội chui tọt qua. Thậm chí làm formal check trên top thì nhiều khi kỹ sư cho khối analog là black box cho tiệnNguyên văn bởi Rommel.de Xem bài viếtỞ chỗ bạn có chạy full-chip simulation cho các thiết kế không? Theo suy nghĩ của tớ thì full-chip simulation có cái dở là chạy rất lâu nhưng cái hay là có thể phát hiện ra các lỗi do những người thiết kế khác nhau suy nghĩ không được thống nhất giống như trường hợp bạn nói. Nếu như khối mà bạn nói đến chỉ là analog thì vấn đề tương đối đơn giản. Các khối analog thường không nhiều lắm và có thể chèn thêm bằng phương pháp thủ công. Vấn đề chỉ là người thiết kế đã quên mà thôi. Theo tớ nghĩ thì full-chip verilog simulation có thể phát hiện ra rất dễ dàng vì sau khi bạn đã model các khối analog thành verilog model, nếu không có điện thì tín hiệu ra là "X". Giá trị X sẽ chạy khắp các khối (khi đầu vào là X thì đầu ra cũng là X) và sẽ phát hiện ngay ra ở đầu ra. Full-chip verilog simulation chạy cũng khá nhanh đơn vị có thể tính theo giờ tùy thuộc vào stimuli bạn đưa vào.

Tất nhiên là có verilog netlist thì hoàn toàn có thể mô phỏng ở mức module để phát hiện ra nhưng dùng công cụ mô phỏng số với các kỹ sư làm tương tự thì cũng có nhiều thứ bất tiện.

Một vài dòng trao đổi thêm,

Thân mến

Leave a comment:

-

Chào bạn Hithere123,

Bạn có thể giới thiệu sơ lược về phần mềm spyglass được không. Tớ chưa bao giờ dùng cái này cả.

Ở chỗ bạn có chạy full-chip simulation cho các thiết kế không? Theo suy nghĩ của tớ thì full-chip simulation có cái dở là chạy rất lâu nhưng cái hay là có thể phát hiện ra các lỗi do những người thiết kế khác nhau suy nghĩ không được thống nhất giống như trường hợp bạn nói. Nếu như khối mà bạn nói đến chỉ là analog thì vấn đề tương đối đơn giản. Các khối analog thường không nhiều lắm và có thể chèn thêm bằng phương pháp thủ công. Vấn đề chỉ là người thiết kế đã quên mà thôi. Theo tớ nghĩ thì full-chip verilog simulation có thể phát hiện ra rất dễ dàng vì sau khi bạn đã model các khối analog thành verilog model, nếu không có điện thì tín hiệu ra là "X". Giá trị X sẽ chạy khắp các khối (khi đầu vào là X thì đầu ra cũng là X) và sẽ phát hiện ngay ra ở đầu ra. Full-chip verilog simulation chạy cũng khá nhanh đơn vị có thể tính theo giờ tùy thuộc vào stimuli bạn đưa vào.

Leave a comment:

-

Chào bạn Rommel.de và bạn themumy

Mạch mình đưa ví dụ trên là thuộc phần analog, và nó chỉ đơn thuần là một ví dụ minh họa cho một trường hợp floating point đặc biệt mà các spice simulation khó có thể phát hiện ra.

Còn power up/down với analog thì tương tự như turn-on/off một mạch tương tự chức năng LDO. Trong IC thường có khối "power management unit" và khối này có nhiệm vụ cung cấp điện áp cho các khối mạch bên trong IC, ví dụ là VDDD và VDDA như trong bài toán của mình. Khi nào bật hay tắt là tùy vào từng trang thái hoạt động của IC, ví dụ sleep mode thi tắt hết mấy cái liên quan nhiều đến xung đi chẳng hạn.

Mình cũng đang nghĩ tới phương án chuyển cdl netlist sang verilog netlist bao gồm cả power. Tuy nhiên sẽ không chạy mô phỏng mà chỉ dùng phần mềm ví dụ spyglass để làm power check. (các lỗi floating mà vẫn còn power thì spice có cách để phát hiện ra nên không cần chạy ở mức top-level). Tuy nhiên nếu có một cách nào đó có thể dùng mô phỏng để tìm ra lỗi do power down kiểu này thì nó sẽ quen thuộc với kỹ sư thiết kế tương tự hơn.Nguyên văn bởi Rommel.de Xem bài viếtĐể chạy mô phỏng một cách kỹ lưỡng tránh xảy ra các trường hợp không ngờ tới người ta dùng verilog full-chip simulation. Trong kiểu này các khối analog được viết lại thành các verilog model và sau đó chạy rất nhiều hoạt động khác nhau thậm chỉ có thể sử dụng kiểu khởi tạo ngẫu nhiên để chạy các loại lệnh, các loại trường hợp một cách ngẫu nhiên. Với kiểu chạy này nếu như có lỗi xảy ra người ta có thể phát hiện ra.

Lỗi mình mô tả ở trên là do có hai kỹ sư thiết kế hai khối VDDD và VDDA, công thêm hai khối này lại là hai khối của một module tương tự nên ở bước kiểm tra top-level đã không phát hiện ra. Đây chính là lý do mình nói: với thiết kế nhiều lớp và do nhiều kỹ sư làm thì những lỗi dạng này sẽ hay gặp.

Thân mến,

Leave a comment:

-

Chào bạn Themummy,

Thật ra tớ cũng chưa được hiểu rõ ý bạn Hithere123 lắm nhưng nếu như bạn nói về việc power up/down của phần số thì thật ra vấn đề không nằm ở isolation cell. Thiết kế isolation cell rất đơn giản không có gì đáng nói. Vấn đề là trong thiết kế số người ta không làm theo kiểu thu công mà tự động tổng hợp mạch bằng các phần mềm EDA. Mạch được mô tả bằng các file netlist. Về nguyên tắc bạn hoàn toàn có thể chèn một cách thủ công như tạo ra một netlist mới bao bên trong netlist cũ và đưa thêm vào các isolation cell nhưng nếu được thì người thiết kế muốn những công việc như vậy cần phải làm tự động. Việc làm tự động sẽ tránh được sai sót vì việc làm thủ công rất dễ gây ra sai sót và khi bạn xem một file netlist cực lớn thì bạn chẳng thể tìm ra lỗi ở đâu. Ngoài ra như tớ nói isolation cell chỉ cần khi tín hiệu chuyển từ phần bị tắt nguồn sang phần đang hoạt động. Tất cả những việc tạo isolation cell, điều khiển isolation cell... cần phải được tạo ra một cách tự động để tránh sai sót.

Lỗi mà bạn Hithere123 nhắc đến có lẽ là lỗi ở khi chuyển tiếp giữa 2 khối. Lỗi này xảy ra khi 2 người kỹ sư thiết kế 2 khối khác nhau. Đối với từng khối riêng thì họ đều đã kiểm tra kỹ nên không bị lỗi nhưng khi đưa vào cả hệ thống thì chúng hoạt động không đồng bộ với nhau vì mỗi người suy nghĩ một cách khác nhau. Tớ lấy ví dụ tớ thiết kế khối A và tớ nghĩ rằng khi tớ làm một công việc nào đó thì tớ có thể cắt bỏ nguồn của khối C. Một người khác thiết kế khối B và cứ nghĩ rằng khối C luôn hoạt động (mà không biết là tớ đã cắt bỏ nguồn). Những lỗi như vậy xảy ra rất phổ biến. Cách phát hiện các lỗi này là chạy full-chip simulation. Full-chip simulation thường chia ra 2 loại. Loại thứ nhất là spice simulation. Loại này chạy rất chậm nhưng chính xác dùng để kiểm tra cả về mặt thời gian hoạt động của toàn bộ mạch. Ngày nay để tăng thời gian chạy, người ta chuyển sang dùng mix signal simulation. Với kiểu mix signal này thì phần analog vẫn dùng kiểu spice simulation còn phần số (chính là các phần tử trong standard cell library) sẽ được chạy verilog simulation. Mặc dù vậy spice full-chip simulation chỉ dùng để chạy các chức năng cơ bản. Để chạy mô phỏng một cách kỹ lưỡng tránh xảy ra các trường hợp không ngờ tới người ta dùng verilog full-chip simulation. Trong kiểu này các khối analog được viết lại thành các verilog model và sau đó chạy rất nhiều hoạt động khác nhau thậm chỉ có thể sử dụng kiểu khởi tạo ngẫu nhiên để chạy các loại lệnh, các loại trường hợp một cách ngẫu nhiên. Với kiểu chạy này nếu như có lỗi xảy ra người ta có thể phát hiện ra.

Leave a comment:

-

chào mọi người,

Em cũng đang ngâm cứ về power consumption analysis nên cũng mún đóng góp một vài ý kiến . Theo em nghĩ thì cách khắc phục vấn đề floating point khi giao tiếp giữa một power-managed block với 1 block luôn on là chèn thêm isolation cell như anh Rommel.de đã đề cặp ở trên. Isolation thì có 3 loại:

. Theo em nghĩ thì cách khắc phục vấn đề floating point khi giao tiếp giữa một power-managed block với 1 block luôn on là chèn thêm isolation cell như anh Rommel.de đã đề cặp ở trên. Isolation thì có 3 loại:

1. Giữ giá trị 0 khi power turn off.

2. Giữ giá trị 1 khi power turn off.

3. Giữ giá trị gần nhất khi power turn off.

Với loại thứ 3 theo như hình vẽ thì phải chèn thêm 1 IV, 3 NMOS và 1 PMOS

Như vậy trong tình huống anh Hithere123 đưa ra thì em nghĩ là phải biết được block VDDD bị turn off khi nào ( sleep signal quản lý power của mạch này ) thì mới giải quyết được vấn đề Túm lại là trách nhiệm thuộc về nhóm thiết kế block VDDD. Hok biết em có nói sai gì hok, mong mọi người chỉ bảo thêm

Túm lại là trách nhiệm thuộc về nhóm thiết kế block VDDD. Hok biết em có nói sai gì hok, mong mọi người chỉ bảo thêm

Em kô hiểu tại khi thiết kế nhiều lơp mạch bị vấn đề floating point?? Mong anh giải thích rõ hơn giúp emMặc dù, hiện nay trong thiết kế mixed-signal thì phần interface giữa các khối với nhau được định nghĩa trạng thái rất rõ ràng khi power down nhưng với thiết kế có nhiều lớp mạch và do nhiều kỹ sư tham gia thì lỗi dạng này vẫn tồn tại.

Leave a comment:

-

Chào bạn Hithere123,

Tớ chưa thật sự hiểu rõ yêu cầu mạch của bạn lắm nhưng tớ nghĩ lỗi này có thể tìm ra được nếu chạy mô phỏng full-chip verilog simulation. Trước khi chạy full-chip verilog simulation bạn phải mô phỏng các mạch tương tự bên trong chip bằng model trên verilog. Trong model này khi không có điện thì tín hiệu ra là 'X' thay vì một giá trị nào đó lúc trước. Điểm này hay hơn ở chạy mô phỏng tương tự vì tương tự chỉ có các mức điện áp. Nhiều khi điện áp lưu lại mức lúc trước nên mô phỏng full-chip không nhận ra dễ dàng. Khi chạy mô phỏng bạn tạo config trên virtuoso và lựa chọn sử dụng model thay vì schematic của mạch, tạo ra full chip netlist, rồi sau đó chạy mô phỏng bình thường.

Có vài điểm tớ chưa được hiểu rõ ý bạn. Thứ nhất mạch của bạn là tương tự hay số. Hai cái này rất khác nhau ở cách thiết kế nên xử lý cũng khác nhau. Mạch số người ta thường tổng hợp mạch còn mạch tương tự thì người ta thiết kế bằng tay. Điểm thứ hai tớ muốn hỏi lại là bạn thật sự tắt nguồn điện sao? Bạn tắt nguồn bằng cách nào, có phải là dùng một transistor dưới dạng switch để cắt nguồn tương tự như phương pháp power gating hay dùng cách nào khác? Nếu như mạch bạn là số thì theo tớ biết việc tắt nguồn người ta thường dùng phương pháp power gating mà thôi; còn nếu mạch bạn là tương tự thì theo như tớ biết người ta không cắt nguồn của mạch tương tự. Mạch tương tự tiêu thụ dòng chủ yếu là bias, chỉ cần cắt các dòng này là đủ rồi.

Leave a comment:

-

Chào bạn Rommel.de,

Mình không nói tới kỹ thuật power gating trong thiết kế ASIC, vì hiện tại những công cụ sử dụng trong ASIC xử lý tự động phần floating point rất tốt (theo đánh giá của mình).Nguyên văn bởi Rommel.de Xem bài viếtChào bạn Hithere123,

Tớ không biết có phải bạn muốn nói đến kỹ thuật power gating hay không?

Ở đây, mình đưa ra trường hợp hai mạch có hai đường cung cấp nguồn khác nhau là ví dụ minh họa cho trường hợp khối mạch VDDD có nhiễu đường nguồn cao, không muốn ảnh hưởng sang khối mạch VDDA nên cần cung cấp riêng biệt hai đường nguồn. Và vì cung cấp nguồn riêng biệt nên nếu không dùng có thể tắt để tiết kiệm. Thêm nữa, thực chất VDDA và VDDD là có điện áp bằng nhau nên cũng không nhất thiết cần levelshift khi nối tín hiệu giữa hai khối này lại với nhau. Tuy nhiên, tiết kiệm được một chút thì nó lại gây ra lỗi floating point như mình đưa ví dụ ở trên.

Thông thường với đặc điểm floating point kiểu khác ví dụ như: VDDD vần còn; M1 và M2 đêu bị tắt dẫn tới net1 floating thì sẽ có cách mô phỏng để tìm ra. Tuy nhiên ở trường hợp này net1 bị floating ở khoảng điện áp ~Vt của PMOS. Chính điều này đã gây khó chịu cho các mạch ở khối VDDA vì quả thật, không đơn giản để tìm ra nó bằng các mô phỏng thông thường. Mục đích của mình đưa ra trường hợp này là để mọi người thảo luận xem có cách gì tìm ra nó trước khi tape-out không.

Đây là kinh nghiệm thực tế mình gặp phải, và nó là lỗi do sự bất cẩn của người kỹ sư vì người kỹ sư không lường trước được khi power down thì có floating ~ Vt như vậy và kết quả là đã gây ảnh hưởng sang khối hàng xóm. Mặc dù, hiện nay trong thiết kế mixed-signal thì phần interface giữa các khối với nhau được định nghĩa trạng thái rất rõ ràng khi power down nhưng với thiết kế có nhiều lớp mạch và do nhiều kỹ sư tham gia thì lỗi dạng này vẫn tồn tại.

Thân mến,

Leave a comment:

-

Chào bạn Hithere123,

Tớ không biết có phải bạn muốn nói đến kỹ thuật power gating hay không? Nếu bạn muốn nói đến kỹ thuật power gating thì đây là một kỹ thuật bên phần số và mô tả như bạn chưa được chính xác lắm. Để tớ mô tả lại một chút cho rõ rằng hơn. Kỹ thuật power gating dùng để giảm dòng điện rò trong phần số của IC. Các công nghệ mới của IC hiện nay có dòng rò rất lớn. Ví dụ như ngày trước tớ có nghe một báo cáo của công ty nói rằng mấy chip bên tớ làm công suất tiêu thụ do dòng rò đã lớn hơn cả công suất tiêu thụ khi mạch hoạt động. Cái này cũng là bởi vì hiện nay người ta muốn giảm công suất tiêu thụ điện nên có phần nào mà chip không hoạt động là người ta cho ngay một clock gating vào đó. Vì vậy mà công suất tiêu thu do mạch chạy thật sự thì nhỏ mà công suất tiêu thụ do dòng rò lúc nào cũng có thì lớn.

Kỹ thuật power gating không phải là người ta tắt nguồn hay giảm nguồn xuống mức 0V. Trong kỹ thuật power gating người ta không nối thẳng các standard cell xuống đất mà chỉ nối vào một đất ảo. Đất ảo này được nối với một số con NMOS rồi mới nối xuống đất. Nếu như các bạn nhìn trên layout thì các standard cell được xếp vào với nhau giống như những cục gạch vậy. Ở giữa các hàng standard cell là 2 đường nguồn và đất ở lớp kim loại M0 chạy song song nhau. Cứ cách một khoảng thì có một số đường nguồn người ta gọi là power strap vuông góc với các đường nguồn và đất mà tớ nói đằng trước cấp điện cho các đường nguồn và đất này từ power ring ở bên ngoài. Các con NMOS dùng cho power gating người ta cũng làm tương tự như một standard cell được đặt bên dưới đường power strap dành cho đất để nối đất ảo của mạch với đất thật ở trên power ring. Sở dĩ người ta dùng NMOS và cách li đất chứ không phải là nguồn vì NMOS dẫn được dòng điện lớn hơn PMOS nên có thể dùng những transistor nhỏ và khoảng cách giữa các power strap cũng xa nhau hơn. Các NMOS này có threshold voltage cao nên dòng rò có thể giảm đi hàng chục lần.

Đúng như bạn nói khi người ta không sử dụng mạch này nữa người ta có thể tắt các NMOS này và khi đó điện áp đầu ra sẽ tăng dần lên mức nguồn nhưng có thể khá chậm và trong thời gian này mức tín hiệu đầu ra có thể làm ảnh hưởng đến các mạch khác. Chính vì vậy người ta phải chèn thêm vào giữa các isolation cell. Các isolation cell này khi bật lên sẽ chặn tín hiệu của đầu ra mạch không cho ảnh hưởng đến các mạch khác. Có một điểm đáng nói nữa là không phải khi nào người ta cũng cần các isolation cell này. Cái này chỉ cần đối với các tín hiệu đi từ vùng bị tắt điện sang vùng đang hoạt động (nếu từ vùng tắt sang vùng tắt, vùng hoạt động sang vùng tắt, hoặc vùng hoạt động sang vùng hoạt động thì không cần). Bên cạch vấn đề các đầu ra người ta cũng phải lưu trữ lại dữ liệu của các flipflop bên trong vùng bị tắt điện vì sau khi tắt nguồn thì giá trị của các flipflop này không lưu trữ được. Người ta cũng không thể chỉ tắt điện các phần khác mà không tắt các flipflop vì chúng đều được layout chung với nhau và sử dụng chung các đường nguồn và đất mà tớ đã nói ở trên.

Thường khi dùng power gating thì việc bật và tắt nguồn cần có thời gian. Dễ nhận thấy nhất đó là ít nhất bạn cần thời gian để tín hiệu đầu vào chạy qua toàn bộ mạch đưa đến đầu ra, rồi sau đó mạch mới có thể hoạt động được. Trong thời gian bật tắt này người ta đọc dữ liệu của các flipflop bên trong ra bên ngoài hoặc ngược lại, bật hoặc tắt các isolation cell. Nếu vùng bị tắt điện có sử dụng DLL để đồng bộ tín hiệu đồng hồ thì cũng có 2 khả năng. Thứ nhất là DLL không bao giờ tắt. Thứ hai nếu DLL tắt thì nó cần có một số chu kỳ để đồng bộ lại với tín hiệu đồng hồ chung. Thông thường các DLL dùng ở đây là loại số nên nó có thể lưu trữ được giá trị trễ tại thời điểm trước khi tắt nguồn. Nếu đưa giá trị này vào DLL thì DLL sẽ đồng bộ lại tương đối nhanh. Tất các các hoạt động bật tắt... đều được điều khiển số bởi controller nên về lý thuyết thì ta không gặp vấn đề gì.

Vấn đề căn bản của kỹ thuật power gating hay việc chèn thêm các isolation cell là ở khâu tự động hóa của EDA. Hiện nay chu trình thiết kế mạch số là sử dụng các công cụ để tự động tổng hợp mạch, tự động layout. Việc chèn thêm các isolation cell này cũng phải được đưa vào chu trình thiết kế này một cách tự động. Về mặt này thì tớ không rõ công cụ nào hiện nay làm tốt công việc này.

Nếu như bạn Hithere123 không phải nói đến kỹ thuật power gating mà chỉ là 2 vùng điện áp khác nhau thì người ta chỉ cần dùng level shifter là đủ rồi. Còn đối với mạch analog thì theo như tớ biết người ta không sử dụng kỹ thuật power gating. Với mạch analog thì người ta thường tắt các dòng bias hoặc các tín hiệu đồng hồ là đủ. Việc tắt dòng bias đơn giản nhất là có thể dùng một switch; trong chế độ hoạt động thì nối cực gate các transistor với drain của current mirror còn khi muốn tắt thì nối cực gate lên nguồn hoặc xuống đất. Khi đó tất cả các dòng bias đều bị chặn lại. Trong trường hợp không thể nối điện áp cực gate xuống nguồn hoặc đất thì người ta có thể đưa vào một switch ngay bên cạnh transistor của current mirror để cắt dòng đi qua. Đối với mạch tương tự, khi người ta cắt dòng bias hoặc tắt tín hiệu đồng hồ thì điện áp đầu ra thường lên mức nguồn hoặc xuống đất. Điều này không làm ảnh hưởng gì đến các mạch phần sau nó.

Leave a comment:

-

floating point

Chào mọi người,

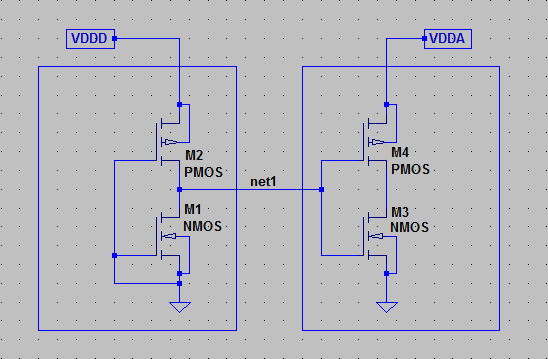

Từ bây giờ thỉnh thoảng mình sẽ đưa lên một vài vấn đề hay gặp trong thiết kế. Vấn đề đầu tiên là về anh "floating point". Đây là một vấn đề rất khó chịu khi làm việc ở mức top-level, nhất là đối với dự án có sự tham gia của nhiều kỹ sư. Ví dụ như hình vẽ mô tả dưới đây:

Giả sử trong một điều kiện làm việc nào đó, điện áp VDDD bị tắt để tiết kiệm power nhưng khối VDDA vẫn cần thiết hoạt động. Ở trường hợp này điện áp tại net1 sẽ đi theo VDDD thời gian đầu nhưng sẽ bị giữ lại ở khoảng ~Vt. Điện áp này thông thường sẽ đủ để gây cho mạch ở khối VDDA nhiều rắc rối, tuy nhiên dòng sai khác lại chỉ khoảng vài uA. Vì vậy mà rất khó phát hiện ra bằng các công cụ mô phỏng thông thường.

Ngoài ra, các bạn có thể tìm hiểu thêm trong thiết kế ASIC thì nó tương đương môt số thuật ngữ hay được đề cập như kiểm tra các power domain bằng spyglass, hay sự cần thiết phải sử dụng định dạng chuẩn UPF (unified power format), ...

Những vấn đề dạng này các bạn có thường gặp trong thiết kế không? và các bạn đã hoặc sẽ có các cách xử lý như thế nào?

Mong nhận được các ý kiến đóng góp từ mọi người!

Thân mến

Leave a comment:

-

Hihi, xem ra các bạn đã chuẩn bị quá tốt về thông tin để đi tị nạn giáo dục rồi còn hỏi tớ làm gì. Tớ chỉ biết một số nét sơ bộ thôi còn cụ thể bạn phải tự tìm hiểu. Chúc các bạn may mắn sớm ra đi tìm đường cứu nước.

Leave a comment:

-

To bác Rommel.de: cảm ơn bác về các thông tin rất hữu ích.

Cái IMEC như trên bác có nhắc tới làm việc rất chặt với K.U. Leuven University.

STMicroelectronics hình như có cả o Ý nữa ạ, không biết học ở Ý thì có phải đóng học phí không ạ?

Bác có biết ở Hà Lan có khóa học nào không ạ?

Ở Bắc Âu em cũng thấy có được miễn học phí như Đức trước đây nhưng em không rõ có chương trình nào giống như bác vừa nói cho sinh viên quốc tế như ở Đức không ạ?

Cảm ơn bác một lần nữa!

Leave a comment:

-

Các bạn nếu đang học đại học ở VN mà bỏ ngang giữa chừng thì phí lắm. Thôi thì các bạn cứ cố học xong đại học ở VN đi và đồng thời chuẩn bị tốt về ngoại ngữ cũng như các thứ khác rồi đi "tây du" sau khi đã học xong. Bằng đại học ở VN sang tây mà xin việc thì không mấy ai coi trọng nhưng mà xin học master thì cũng OK. Ở châu Âu có nhiều chương trình master cho sinh viên quốc tế. Thông thường sinh viên của các chương trình này đến từ Tung của, Ấn Độ, mấy nước châu Á, châu Phi, Mỹ Latinh nên bằng đại học ở VN dù chẳng ra gì thì bằng của bọn này cũng không hơn gì các bạn. Nói chung cơ hội được chia đều cho các bên. Các chương trình này ở châu Âu nhằm thu hút sinh viên từ các nước khác nhằm tăng cường một quan hệ giữa các nước nên nó không yêu cầu sinh viên vào đã phải suất sắc (nếu là sinh viên của các nước tiên tiến thì họ đã không theo mấy chương trình này). Nó cũng giống như việc đào tạo người dân tộc hay vùng sâu vùng xa ở VN vậy. Nói như thế cũng không có nghĩa chất lượng mấy chương trình này kém. Mặc dù là chương trình riêng nhưng việc học là chung vơi tất cả các sinh viên theo kiểu tín chỉ. Ai thích đăng ký học gì thì học. Một điểm nữa là nhiều chương trình như vậy dạy bằng tiếng Anh (cho sinh viên quốc tế mà).

Ở châu Âu về mặt điện tử đương nhiên mạnh nhất là Anh, Pháp, Đức rồi. Riêng nước Anh nằm tách biệt so với liên minh châu Âu và thu học phí rất cao nên chắc nhiều bạn sẽ không lựa chọn. Pháp nổi tiếng có hãng STMicroelectronics, Đức có hãng Infineon Technologies chắc các bạn đều biết. Bên cạnh Pháp và Đức thì ở Bỉ có viện nghiên cứu IMEC thuộc vào loại hàng đầu thế giới về vi điện tử. Viện này làm việc rất chặt với một trường đại học mà tớ quên mất tên rồi. Tuy nhiên viện IMEC hình như tập trung nghiên cứu chủ yếu là công nghệ vi điện tử chứ không phải là thiết kế vi điện tử (công nghệ chế tạo chip). Thụy Sỹ cũng có trường ETH zurich (Đại học công nghệ liên bang Zurich) cực kỳ tốt và nổi tiếng.

Giáo dục ở Mỹ thì lại hoàn toàn khác. Họ không có một chương trình riêng cho sinh viên nước ngoài, và họ coi tất cả sinh viên là như nhau. Ở Mỹ yêu cầu đầu tiên để được vào học là "tiền đâu", sau đó mới là trình độ của bạn. Việc xin các loại hỗ trợ về tài chính như TA, RA, hay scholarship thường chỉ dành cho PhD, và yêu cầu bạn cần có trình độ cao + may mắn. Ở Mỹ cũng có cái là có rất nhiều trường đại học nhưng cũng rất nhiều trường lởm. Ở châu Âu thì chất lượng tương đối đồng đều.

Có một điểm nhỏ tớ có thể nói thêm là rất nhiều trường cho phép các bạn nộp hồ sơ từ khi chưa tốt nghiệp đại học xong. Ví dụ như bạn đang học năm thứ 5, chưa tốt nghiệp nhưng dư định sẽ tốt nghiệp vào tháng 7 chẳng hạn. Bạn đã có thể nộp hồ sơ ngay từ tháng 3 để được xét, rồi sau đó còn cần thời gian làm các thủ tục khác nhau như xin visa để tháng 9 là có thể vào học ngay.

Leave a comment:

-

Bác Rommel khuyên chúng em nên đi "tây du" luôn từ bậc đại học, hay học xong đại học ở VN rồi đi học tiếp ạ.

Nguyên văn bởi Rommel.de Xem bài viếtChào bạn Ngoclinh_xl,

Thật sự thì chính tớ mới phải ngưỡng mộ các bạn thì đúng hơn. Lúc tớ học năm thứ 3 thì đến mấy công cụ của cadence, synopsys tớ còn chưa được nghe nói đến chứ nói gì đến việc thiết kế. Thật sự là bây giờ các bạn đã có điều kiện tiếp xúc với những công nghệ hiện đại hơn tớ ngày xưa rất nhiều. Nếu có điều kiện các bạn cố gắng đi "tây du" để phát triển thêm (tớ bắt chước cụ Phan kêu gọi thanh niên )

)

Tớ được may mắn học dưới mái trường xã hội chủ nghĩa và cũng không may mắn ăn phải bả tư bản nên tớ biết so sánh và thấy ăn phải bả tư bản thì sướng hơn . Các bạn cứ từ từ rồi kiểm chứng.

. Các bạn cứ từ từ rồi kiểm chứng.

Leave a comment:

Bài viết mới nhất

Collapse

-

Trả lời cho Yêu thơ mê nhạc, mời các bác vào đây!bởi vi van phamCháu nghe thử trên youtube xem sao? : https://www.youtube.com/watch?v=Opm0BszTmFQ...

-

Channel: Tâm tình dân kỹ thuật

Hôm qua, 21:23 -

-

Trả lời cho Yêu thơ mê nhạc, mời các bác vào đây!bởi dinhthuong92Cháu không vào được để nghe thử. Mời bác nghe thử bản phối điệu Techno này xem thế nào nhé! Chúc bác vui.

( Cháu nhìn lyrics và cứ thế một mmạch hát demo rồi đưa vào suno. nó hát đạt 80% melody!)...-

Channel: Tâm tình dân kỹ thuật

27-04-2026, 17:00 -

-

Trả lời cho Yêu thơ mê nhạc, mời các bác vào đây!bởi dinhthuong92Bài này cháu phải "Creat" trên 30 lần rồi cắt ghép mới tạm có hồn tí đó bác. Quá nản luôn!!!

HẸN ƯỚC XUÂN SANG

Sáng tác: Hoàng Đình Thường

Hòa âm & hát: Suno AI

---25/04/2026----

[Verse 1]

Gió...-

Channel: Tâm tình dân kỹ thuật

25-04-2026, 11:05 -

Leave a comment: